2023.7.31

- 2023年7月16日11点13分,浙江绍兴,上虞南站。 兴奋、期待、忐忑……不知道应该用什么样的词语来形容我此刻的心情,这是我第一次,孤身一人,来到一座陌生的城市。公司环境会是怎样,新舍友怎么样,同事们怎么样,工作究竟会不会做……无数的想法充斥着我的脑海里,但是这是一次全新的体验,因为这意味着第一次走出学校,走进社会。 在火车站等公交车等了半小时竟然都等不到一辆,我只好打车来到中芯集成,并在一番折腾后终于拖着重重的箱子,满头大汗并忐忑地敲开了新宿舍的门。 “hi~,我是你们的新舍友。”

- 我的三个新舍友都是研二的学生,也是暑假来实习的。由于他们都比我大了好几岁,并且我本身就比较内向与社恐,刚开始跟他们交流的时候就显得有点胆怯(可能不止一点),尽管他们都非常的友善。当他们惊叹于我大二就来实习的时候并且是fdu的学生时,我连忙摇头摆手说自己很菜。我从小到大都是这样,过于内敛,害怕被人夸赞,但实际上虽然谦虚是好事,可是有时候就应该大方自信一点。反思过后,我认为再来一次的话应该要这样子回答: Q:大二就来实习了吗? A:对,早点来实习长长见识! Q:你是fdu的啊?牛逼 A:哈哈哈还行吧,以后还得向你们多多请教呢!*

- 我被安排到的部门是 Technique & Marketing Centre - Design Enablement - Spice Model - HV/Anolog SPICE,职位是 HVS。带我的周扬师兄,以及其他所有同事都很热情友善,整个小组氛围也很好。但可能还是因为年龄差的原因,并且我觉得我没有一点工作经验以及对于能否做好实习的工作缺少底气,我和同事们交流的时候还是放不开,不太自然(自己听自己的声音都能明显感觉得到)。唉,树安,下次自信一点,展示一下fdu高材生魅力,how say!

- 第一个星期还没配好电脑,于是自己看了看书,复习了一下半物和模电,在b站上学了点强化学习;第二个星期终于等来了电脑,但是周扬师兄让我先看下培训资料,讲的是一些器件原理,仿真、测试原理和流程,公司的工艺平台,等等,还是学到不少东西。

- 星期五晚上和同事们一起出去吃顿海鲜自助餐😋😆 明天,八月!

2023.8.6

- 上一周学会了如何用hspice仿真电路,学会了看懂一点点网表并且尝试自己写了一下(其实不知道对不对),学会了看版图,学会了Resistance Extraction的流程。In my opinion,写网表和绘版图还是有点技术含量的,但是学会用excel绘图也还是有用的(还没学,下周研究下)。其实有很多测试的原理也没有完全搞懂,但是其实不是很重要,因为这里的很多工作都是非常完善的,无需从原理研究起来,并且来实习也不是为了学原理和技术。

- 对于待人接物(对于陌生人和一些不是很熟很交心的朋友)的方式又有了深刻的体会:首先要自信,这意味着,气场要强大,有自己独立思考的能力,有自己的想法,不能显露出自己的情绪,要时刻保持冷静和理性;其次是尊重别人,微笑,gentleman。

- 据我猜测,在这个岗位上的正式员工,应该是一两万一个月左右,工作不会很多,压力不会很大,有一定的技术含量,这样一个年能有个二十来万。实习摸鱼的时候,我在思考这样的问题,假设以后毕业出来打工,一年能有五十万,虽然确实已经挺好了,但还是无法十年内全款买房。怎么样,才能实现真正的跨越?我目前想到的只有以下三种方向:创业/从工程师到高管/投资(当然应该在有稳定的较好的工作的基础之上)。前两种的一个前提是,技术本身要够硬,专业知识够强;前两者都要具备创新能力,并且创业更需要创新。第二种则需要很好的管理能力。创业难度大,风险高,需要技术与机遇,综合考虑人脉、市场等因素;而成为企业高管,需要提升自己全方位能力。投资暂未了解。

- ok,上面一段都是瞎jb讲的。

- 今天是tfboys十周年之约,虽然我也不完全算是四叶草,但是我感觉他们(无论是团体还是个人)确实都有很多很好听的歌,并且有些歌真的让人充满能量(比如样YOUNG)。十年之前,我也没想到十年之后是怎么样的,我现在也无法设想十年之后,这个世界,身边的人,自己,还有tfboys,都会变成怎么样。

2023.8.11

实习终于结束了!明天就回家了!前两天写了篇实习报告给赵总看,听说还被赵总传阅了,树安你是有点东西的。

实习报告

实习记录

- 2023年7月18日,我来到了绍兴中芯集成电路制造股份有限公司,开启了我人生中的第一次实习。

- 7月18日是实习报道日,办理入职手续和参加新员工培训,培训内容包括对公司介绍、总务情况、消防安全等等。

- 7月19日,我来到我的工作岗位上正式开始我的实习之旅。我的部门是 Technology & Marketing Center - Design Enablement - SPICE Modeling - HV/Analog SPICE,岗位是 HVS,即负责器件的 SPICE 测试,仿真与建模。一开始还没有申请到电脑,于是我看了两三天书,复习了一下半导体器件原理,听了一些培训讲座。

- 7月25日申请到电脑后,看了几天公司内部的培训资料,ppt,平台手册等,了解了整个岗位的基本任务和操作。

- 7月28日,给电脑安装好工作需要用到的软件后,终于可以开始动手操作,边做边学,如用 Hspice 仿真,进行 Resistor 参数的抽取建模,等等。

- 实习期间,还到实验室观摩了带教师兄进行WAT测试,亲眼看到了晶圆的样子。每周开例会我也都参与了,深入理解了我们SPICE MODEL组,甚至可以说是整个公司的工作,皆是以客户需求为核心,以市场为导向。

实习收获

- 扎实的学科基础是做好实习工作的前提条件。比如,进行WAT测试,当然得先知道要进行测试的电学特性都有哪些,并且需要非常熟悉各种半导体器件(如MOS,BIT,Diode等)的基本原理,这样在进行分析与测试时才能熟练地运用上去。这些知识都是在学校里习得的,也就是说专业知识一定要扎实,并且沉淀为自身的“常识”。

- 但实习时仅靠在学校里学过的知识是远远不够的,因为工作是一种对知识的运用,并且还会涉及许许多多没有学过的知识。这也是为什么公司要对新员工进行入职的培训。但是工作中会遇到非常多的问题,单靠培训获得的知识也是难以 handle 的,这就需要在整个工作中都要具备汲取新知识的能力,边做边学,学以致用。

- 实习第一天,我对于做些什么,为什么要这样做,应该怎么做,没有一点概念。但慢慢的,我逐渐搞明白了这三个问题。从逆向的逻辑来看:我们要做的是SPICE Model的仿真与建模,因为这是芯片设计到物理实现的重要桥梁:芯片设计好后进行物理实现要用到的元器件等,由PDK工具包来提供,而产生PDK前的关键步骤就是进行SPICE Modeling,包括器件的有关方程与参数。那么我们该如何完成这项工作呢?这就需要获得两部分数据:理想的 target 与实测的 value,然后再进行数据分析、拟合并建模。这让我明白了,无论是实习工作,还是处理其他的事情,都需要搞清楚,what, why, how。

- Communication & Corporation。小组内部每周会开一次例会,总结上周工作,提出一些新问题,并布置下周任务;平时同事们也经常探讨问题,发邮件、发信息、打电话联系其他部门的同事,以更好地进行团队合作与工作上的协调。Partnership,是公司文化中四大理念之首,这也是我这段实习中感觉最有收获的地方。因为我一直以来都不太擅长与人沟通,甚至害怕跟陌生人交流。而这次实习给了我一个改变自己的机会,慢慢走出我的 comfort zone,去认识新同事,去向比我年纪大、经验丰富的前辈请教。总之,我明白了待人接物除了要谦虚礼貌外,更要充满自信。当然我还需要更多地锻炼,学习如何更有效地与人沟通交流,进一步学习如何管理好一个团队。

- 当然,在整个实习和培训过程中还学习了许多学术上的知识和技能(详见实习笔记部分):

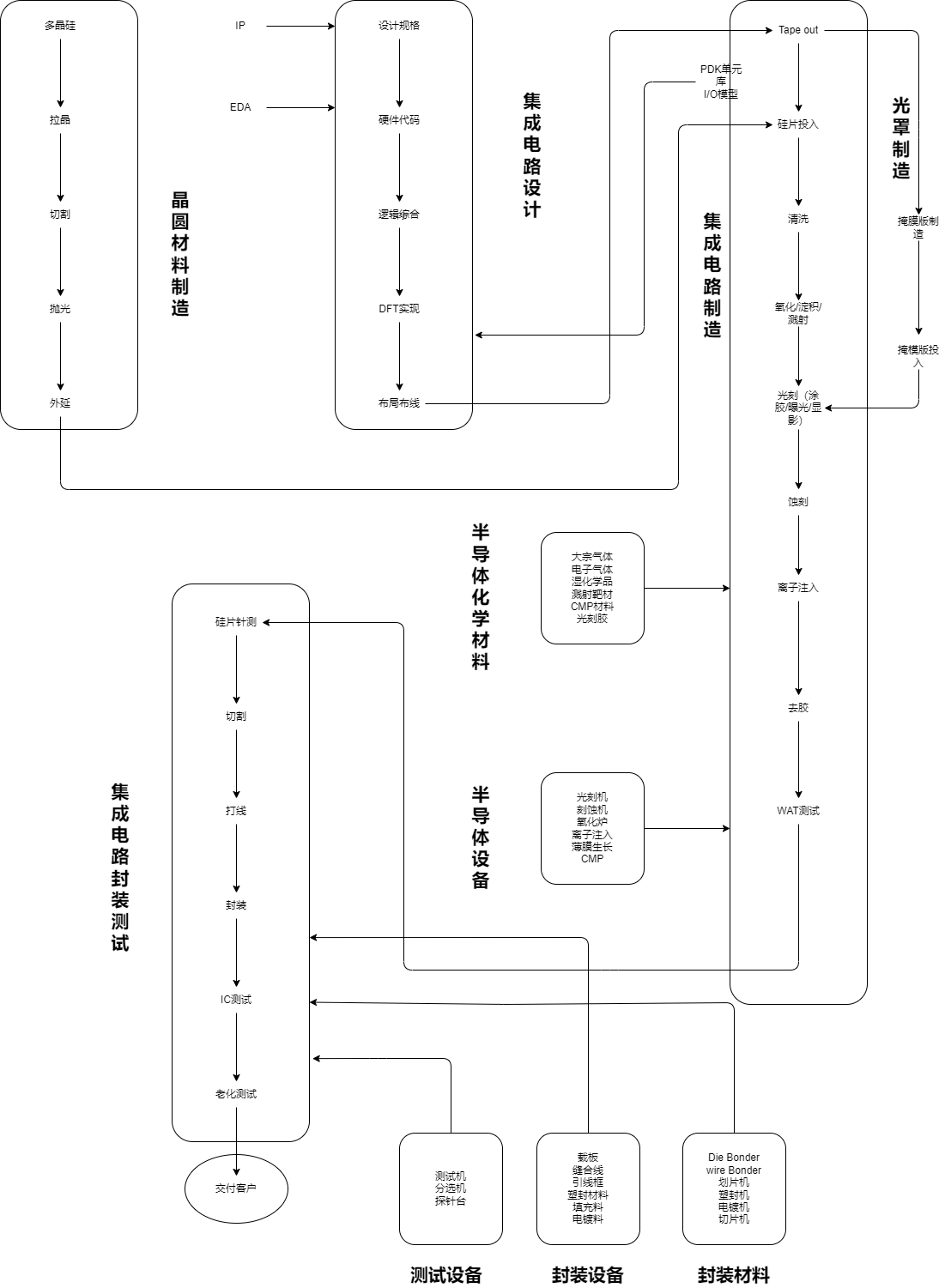

- 对半导体整个产业链、芯片设计制造封装整个流程,有了更深的认识;

- 深入了解了公司的Smec BCD_Platform, 体验了实验室 WAT 测试过程 ,学会了使用hspic进行仿真,KLayout查看版图;

- 基本 Device 的电学性能与测试原理,网表、版图的基础知识;

- 许许多多的集成电路英文专有名词。

实习感想

- 人生中第一次到大厂实习,真的非常开心。特别是当我拿到工牌、坐上属于自己工位的那一刻,顿时感到自身价值倍增。

- 这次实习见识到了一个大公司究竟是怎么样的:首先在部门设计上,大概分为 TMC, Supporting Center, 运营中心,等等,分工明确,各司其职,并且内部还分为多个级别,并有相对应的主管;其次是OA系统,支撑着各种事务的正常运作;然后是部门之间的沟通方式多渠道,电脑端 Skype for Business 即使通讯,Outlook 邮件联系,手机端企业微信,还有平时在部门里面能用座机打电话联络,这些都使得一个拥有5000多名员工的大公司内部能够进行正常有效便捷的交流;而最令我印象深刻的是,公司的保密、信息安全工作做得相当严格,个人的笔记本、平板电脑都不能带进工作区域。总而言之,来到国际大公司、大厂上班给我带来的感觉还是相当的震撼。

- 公司的饭堂算是比较实惠,菜的品种也较为丰富,价格与复旦饭堂差不多,口味也相当不错。宿舍环境超好,四人间比复旦的宽敞多了,还有独立卫浴,干净舒适,唯一的缺点是没有热水饮用。公司的其他硬件设施也非常完备,但是在环境方面,每到傍晚六点多左右,厂房排出来的废气带着一些异味,空气质量下降,感觉再吸多几个星期会少活那么个几年。

- 新人入职培养方面,公司的培训计划与一对一的老带新制度可谓是非常完善和周到,能让新员工快速入门与适应工作。但我觉得培训时间还是太长了点,坐我旁边的一位老哥是新来的应届毕业生,入职一个月了还没什么事情做,还在培训阶段,看各种资料。其实我觉得这个岗位的话一两个星期基本上就能掌握一些核心的原理与操作了,很快就能上手干活,其它的完全可以边做边学。

- 在实习中发生了一件让我比较难受的事情。办理离职申请手续需要经过比较多的审核,整个流程很长比较慢,这很正常。但是如果它卡在了一个节点三四天不动,就让人很难受。8月4号13:02:19到信息安全中心进行审核,8月7日下午17:00还没审核完。于是我联系了对应负责人询问情况,问他是否可以快一点,他答应帮我催促一下。第二天早上9点半,审核还是卡在那里一动不动,于是我又在 Skype for business 上发消息给负责人,想问一下审核进行得怎么样。最让人气愤的是,这名负责人状态是在线at work,但是并没有回复消息。我又发了好几条信息恳求他能否帮忙催促一下,并且提出希望他看到信息可以回复一下,结果还是没有答复。我在企业微信和Outlook上联系他依旧不回。我还真不信他这么忙没有看到消息,于是我在OA系统上找到他的主管,和他说明了情况,请他帮忙联系一下。幸运的是那名主管人比较好,立刻在企业微信里面把我们三人拉了个群,并且 @ 那名负责人,那人立刻出现回复说好,并在不到三十分钟内就完成了审核。这很明显就是那人拖着不去审核,明明几十分钟就能完成的事情拖了好几天,办事效率极其低下,如果不是找到主管督促都不知道还要拖几天;关键是态度极差,之前答应说帮忙催促显然就是敷衍,而且看到消息不回素质非常差;这可能也是公司比较大的缘故吧,监管不到位,导致总会有人做事拖拖拉拉的,一定程度上降低了整个公司的办事效率。

总结

总之,非常感激这段实习经历,给我带来的学习上、能力上、生活上的各种收获,得到一次从未有过的人生体验。衷心感谢师兄赵奇总经理给予这样一次提升自我的机会!祝愿中芯集成越做越好!

附:实习笔记

PDK

- PDK(Process Design kit) is the bridge between foudary and Design house

- PDK = SPICE MODEL + Pcell(Parameterized Cell Library) + Layout Designs + RC/PEX(parastic Resistance and Capacitance extraction)

SPICE Model

- SPICE Modeling flow: Testkey Designs(BaseTK(DC数据), ROTK, AC-Cox/CGC TK) -> T/O and Production -> Measurement(WAT) -> Curve Fitting -> On-target Fitting(LDE Fitting, flicker(1/f) noise fitting, mismatch Fitting, corner Fitting) -> Statistic Fitting -> Model Document -> Model release

- SPICE Model content: a series of equation + corresponded parameters eg. MOS model equation + MOS model card

WAT(Wafer Acceptance Test or E-Test)

- Inline WAT(后段工艺)or Final WAT(全部工艺完成)

- 测量的是:DUT(Device under Test) Active Device: MOS BJT Diode Passive Device: RS RC Capacitor Process: Isolation Bridge

- the relationship among WAT, SPICE Model, PDK: TS Device provide golden wafer -> Spice Testing(WAT) -> Spcie Modeling -> Generate PDK -> CTM IP design in (pre/post-simulation)

- 测试程式:WAT CIM系统 (Test + Prober) Tester: tst(Test condition), lim(Spec), waf(Site location), die(Test key location), prb(PIC to Channel Mapping) Prober: Probe Card Alignment, Wafer Alignment

- 测试结构和参数 Resistor: RS(Rs Rskv), RC(Rc Rckv) Capacitor:Cap(MIM MOM Varactor), Ileak, Vbd Inductor, Contimuity, Bridge, Isolation(介质隔离, LOCOS隔离, STI, Guard Ring, DNWring, Sealring) Diode: Cg, Leak BJT: Vbe β Vce Mosfet: Vt Id Ioff Bvds Swing Cgg Cgc Cgs DIBL Vhg Rout .etc Cmos: Vtc Ring Oscillator: Freq SRAM: IDDQ SNM WM Iread Iwrite

- 先进测试工艺 Array-based Test Structure, share pads among DUTs

- DUT

- Resistance: RS(Resistance Square): to monitor metal/dielectric film resistance Film type: Metal(interconection), AA(N+, P+, Salicide), Poly(N, P, Salicide), Well, STI Rm=V/I=(ρ/T)(L/W), Rs=ρ/T=Rm(L/W) (T:thickness, Rs is for 2-terminal, Rskv is for Kelvin Structure) RC: to monitor the contact/via with the under layer

- Capacitor: Cap@ 100kHz, 45mV, VH=0V, VL=0V, Cap=Cap*(1e+15)/Area Vbd: Search Vh from 0 to 15V @ Ih=4e-8A, H= sweep V, L= GND Ileak: Ilk@ Vh=Vdd

- Continuity: to verify a continuous path in the circuit, if a variance of Rs in the layer or the pattern is open, it can be detected

- Bridge: a bridge means a short between two patterns in the same layer due to an isolation defect(Errors during the mask or etch step)

- Diode: DC current-Voltage characterisic

- BJT: DC, AC caracteristic

- SRAM

- CMOS: DC current-Voltage characterisic, VTC 曲线偏移

- Ring Oscillator: Frequence, 即时钟频率

- MOSFET: DC characteristic: 转移特性,id-Vds Backup Materials: DIBL(Drain insuced barrier lower), Vtsb(Vt @ saturation region wi Body effect), Swing, IDVG, Jginv, GIDL(gate induced drain leak), Idlin, Ioff, Rout, BVDS(击穿电压), Isub(热电子引起基底电流) AC characteristic: cgc, cgb, cgg, 寄生电容等

Corner

- 芯片延迟由 PVT(Process, Voltage, Temperature) 影响

- Process corner 工艺角,包括:

- global variation 全局工艺偏差,同一器件在不同芯片上的误差

- local variation 局部工艺偏差,同一器件在同一芯片上不同区域的误差

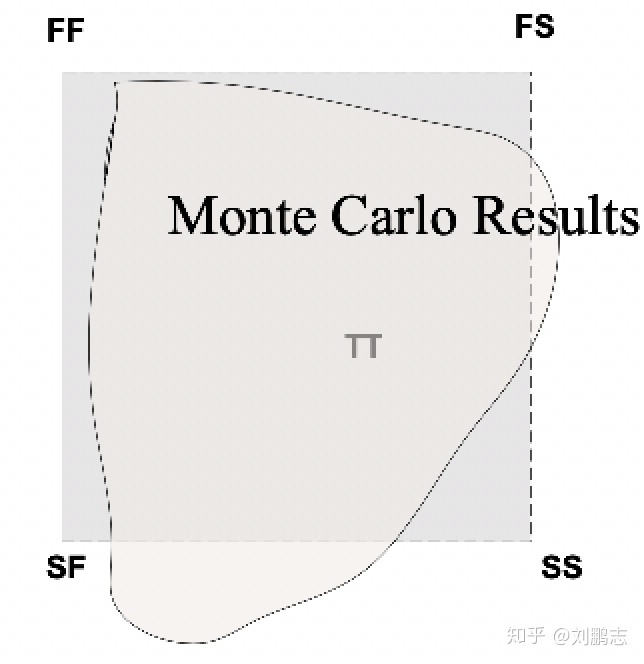

- global variation: tt(typical nmos and typical pmos), ff, ss, sf, fs (s 代表 slow,电流小;f 代表 fast)

- Corner 仿真实现:STA(Static Timing Analysis)

- Monte Carlo 仿真:在容差内随机运算几千次或更多

Hspice 仿真

- 是一个电路仿真eda软件,以网表为输入

- 网表编写(.sp文件)

- 包括元器件描述语句,输入控制语句,输出控制语句等

- .DATA

- .DEL LIB

- .INCUDE

- .IC .NODESET

- .LIB

- .MODEL

- .OP

- .OPTION

- .PARAM

- .TEMP

- .TF

- .TRAN .DC .AC

- .PRINT .PLOT .GRAPH .PROBE .MEASURE

- .end

- 例如 M1 ADDR STG1 GND SBS N1 10u 100u 规定了一个名字为M1的MOSFET,漏极、门极、源极、衬底的节点分别命名为ADDR STG1 GND SBS,参考名为N1的Model,width=10μ吗,length=100μm

- .LIB表示库,连接到.lib文件中,网表里的一些元器件需要从里面找对应的model

- 文件结尾为.end

- .TRAN .DC .AC 分别为瞬态,直流,交流分析

- .PARAM 为定义各种参数,可理解为define

- .OPTION设置条件

- 等等 网表编写可认为是一门语言,需要细细研究

- 包括元器件描述语句,输入控制语句,输出控制语句等

- SPICE 测试后得到数据,进行 SPICE 建模,完成后得到器件所有参数,即可打包成一个文档,以库(.lib)和参考模型(.model)的方式提供给所需网表(.sp)供hspice进行仿真

Resistance Extraction

- parameters:

- Rsh: sheet resistance

- DW, DL: Delta width and length

- TC1R, TC2R: temperature coefficient

- RVC0, RVC1, RVC2: Voltage coefficient

- JC1A, JC1B, JC2A, JC2B: Current density coefficient

- COX, CFOX, CWAPSW, CLOUP: interconnect parastic capacitor

- equations:

- R=R0k1k2

- R0=Rsh*(L-2DL)/(W-2DW)

- k1=1.5-1/(2+RVCVV), when k1 > 1 0.5+1/(2+RVCVV), when k1 < 1 RVC=(RVC0+RVC1W+RVC2L/W)/(L-2DL)/(L-2DL)

- K2=R0(TC2RDTDT+TC1RDT+1) DT=T-T(25°C)

- extractions:

- examine R @ V=0.1V, T=25°C, then optimize, get Rsh, DL, DW

- examine R @ T=25°C, sweep Voltage, get RVC0, RVC1, RVC2

- examine R @ V=0.1V, sweep Temperature, get TC1R, TC2R

- mismatch extraction

- corner extraction

- parasitics capacitor extraction

- model: .lib .sucket

Layout Designs

- 版图将电路映射到硅片,是电路功能和性能的物理实现

- 包括基本元器件版图设计,模块设计->芯片规划->布局布线,版图检验分析(DRC(design Rules Check), LVS(Layout Versus Schematic), 电学可靠性检查(ERC, ESD))

- 绘图层

- N well

- Active: 有源层,需要进行场氧(Oxide)

- Poly: 多晶硅栅层,互连,生成电阻等

- P select, N select: 注入离子,与有源层形成扩散区

- Contact: 接触孔层,存在一定阻值,用于连接金属层与目标层

- Via: 通孔层

- Metal: 金属层,互连

- Text: 文字标注层

- Pad: 焊盘层,提供芯片内部信号到封装接脚的连接

SMEC BCD Platform

- 工艺平台,high density, high power, high voltage features: 完整的BCD技术,高附加值器件,高车规模质量,专业的设计支持

- IPS: 标准BCD工艺/器件 + 嵌入式特色工艺/器件(Vertical) 180 BCD eflash: 标准BCD工艺/器件 + ESFI(3 more masks) BCD-SOI: 使用SOI(Silicon-On-Insulator) Substrate(一种工艺) HVIC: 高压(hig voltage)集成电路

- PDK & IP for Industrial and Automotive

- SPICE MODEL: environment temperature range for modeling, Mos Aging Model for Simulation

- PDK: DRC & Pcell, EM

- IP: Reliability, Functional, Safety

- Quality: QMS of FTP R&D organization, Quality Manual of QMS for R&V organization

- Readiness: Indurial, Automotive G0/G1

- 180nm BCD 40V SPICE

- SPICE Model: Spectre/Hspice/ACPS(即所支持的建模eda工具)

- PDK: Cadence OA PDK

- IP: Standard Cell library, GPIO, Memory Compiler, e-fuse, MTP, OTP, e-flash

- document example

- Title: 0.18μm HVIC 120V platform introduction and charater design mannual

- Purpose: this design mannual defines...

- Scope

- Nomenclature

- Reference

- Responsibility

- Subject Content

- Introduction: Document Overview, Process Overciew, Supported potentials, Device Size Setting in Model & PDK, Effect in Spice Model

- Device Characterization Summary: Device description, Operation voltage range, Device symbol, layout, Cross section, Spice data vs PCM spec

- CMOS, HVMOS(DEMOS, LDMOS, DMOS(VDMOS, DDDMOS)), BJT, Diode, Resistor(DIFF, POLY, NW, Metal), ESD Diode/BJT, Capacitor(MIM, MOM, Varactor), IGBT(MOSFET + PNP, VDMOS + PN junction), .etc

半导体行业情况

半导体产业链全景

半导体产业模式

- IDM(Integrated Device Manufacture): Sumsung, Intel

- Fabless: 海思, 联发科

- Foundry: SMIC, 日月光

半导体PRODUCT市值

半导体产品($4688亿)包括 集成电路($3933亿)+ O-S-D($755亿),其中,集成电路 包括 模拟电路($588亿)+ 数字电路($3345亿)

IC Products

- Memory:

- voliatile(易失性): SRAM(LPSRAM, HS SRAM, eSRAM), DRAM(FP/EDO, SDRAM), DDR(Rmbus, eDRAM)

- non-voliatile: Flash, EPROM/EEROM, MaskROM, MRAM, embedded(Smart Card, National ID)

- Logic:

- computing: CPU, MPU, DSP, DPU, Chipset, Graphics, Peripheral, Mem controller

- consumer: PDA, GPS, MPEG, DVD/VCD, FPGA, Voice synthesis

- Automotive: MCU, Sensor

- Mixual signal:

- computing: audio processor

- communiting: Switching, Sonet, phone, fax, LAN, Router, Bluetooth, Cellular(GPS, CDMA), Modern(xDSL, Cable)

- Photo Electronics:

- Image Sensor: CCD, CMOS

- Display: LCD driver, LCD controller, μ-Display

- Security: Touch chip